# SGM6611C 12.6V, 7A Fully-Integrated Synchronous Boost Converter

## **GENERAL DESCRIPTION**

The SGM6611C is a fully-integrated synchronous Boost converter. The 2.7V to 12V operating input voltage is suitable for single-cell or two-cell Li-Ion/Polymer batteries. This device is capable of providing 7A continuous switch current and an output voltage range of 4.5V to 12.6V.

The SGM6611C has two operation modes, the pulse width modulation (PWM) mode and pulse frequency modulation (PFM). The PWM mode is applied at moderate to heavy load. The PFM mode is applied at light load to improve the efficiency. The protection features include output over-voltage protection at 13.2V, cycle-by-cycle over-current protection and thermal shutdown. The device also involves the functions of 4ms built-in soft-start and adjustable switch peak current limit.

The SGM6611C is available in a Green TQFN-2×2.5-11L package.

## **FEATURES**

- 2.7V to 12V Input Voltage Range

- 4.5V to 12.6V Output Voltage Range

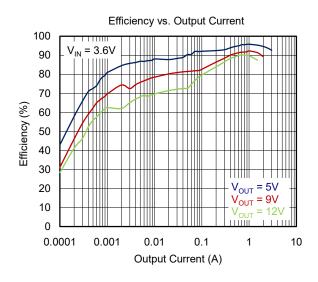

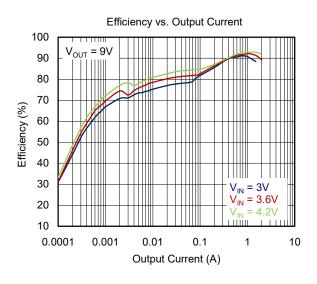

- Up to 90% Efficiency (V<sub>IN</sub> = 3.3V, V<sub>OUT</sub> = 9V and I<sub>OUT</sub> = 1.5A)

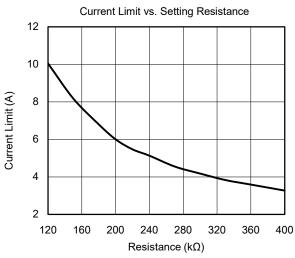

- Adjustable Peak Current Limit up to 9.5A for High Pulse Current

- 1.1MHz Fixed Switching Frequency (PWM Mode)

- 4ms Built-in Soft-Start

- PFM Operation Mode at Light Load

- 13.2V Internal Output Over-Voltage Protection

- Cycle-by-Cycle Over-Current Protection

- Thermal Shutdown

- Available in a Green TQFN-2×2.5-11L Package

## **APPLICATIONS**

Portable POS Machine

Bluetooth Speaker

E-Cigarette

Fast-Charging Power Bank

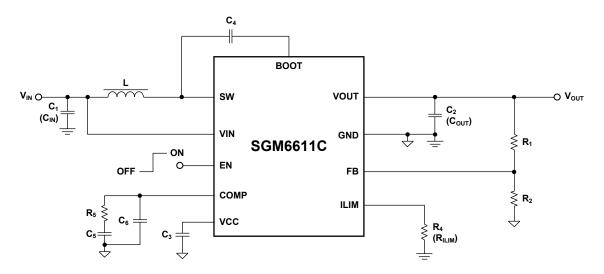

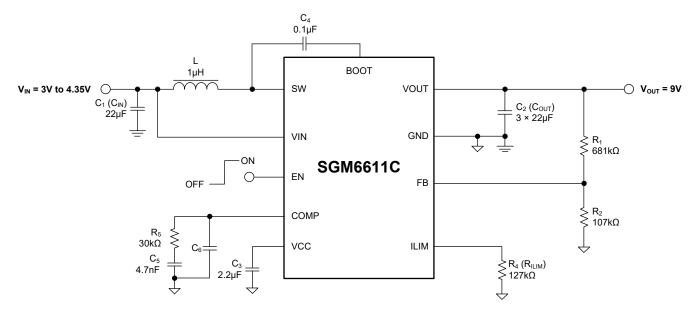

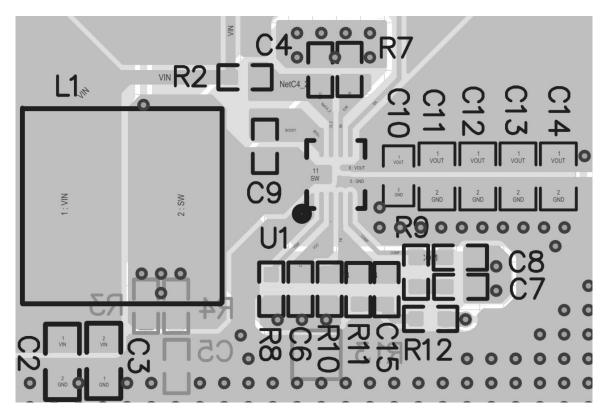

### TYPICAL APPLICATION

**Figure 1. Typical Application Circuit**

## PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM6611C | TQFN-2×2.5-11L         | -40°C to +85°C                    | SGM6611CYTQV11G/TR | 6611C<br>XXXXX     | Tape and Reel, 3000 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| BOOT Voltage0.3V to V <sub>SW</sub> + 6V   |

|--------------------------------------------|

| VIN, SW, VOUT Voltages0.3V to 14.5V        |

| EN, VCC, COMP, ILIM, FB Voltages0.3V to 6V |

| SW Node (Transient: 10ns)2V to 16.5V       |

| Package Thermal Resistance                 |

| TQFN-2×2.5-11L, θ <sub>JA</sub>            |

| Junction Temperature+150°C                 |

| Storage Temperature Range65°C to +150°C    |

| Lead Temperature (Soldering, 10s)+260°C    |

| ESD Susceptibility                         |

| HBM1500V                                   |

| CDM1000V                                   |

#### RECOMMENDED OPERATING CONDITIONS

| Input Voltage Range                           | 2.7V to 12V       |

|-----------------------------------------------|-------------------|

| Output Voltage Range                          | 4.5V to 12.6V     |

| Inductance, Effective Value, L                | . 0.47µH to 2.2µH |

| Input Capacitance, Effective Value, CIN       | 10µF (MIN)        |

| Output Capacitance, Effective Value, $COUT$ . | 10μF to 1000μF    |

| Operating Junction Temperature Range          | 40°C to +125°C    |

| Operating Ambient Temperature Range           | 40°C to +85°C     |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

## **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

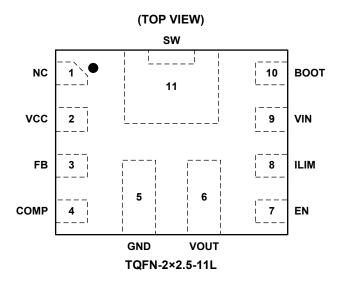

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN | NAME | I/O | FUNCTION                                                                                                                       |

|-----|------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| 1   | NC   | I   | No Connection.                                                                                                                 |

| 2   | VCC  | 0   | Output of the Internal Regulator. The VCC pin connects a ceramic capacitor (> 1.0µF) to ground.                                |

| 3   | FB   | 1   | Feedback Output Pin.                                                                                                           |

| 4   | COMP | 0   | Output of the Internal Error Amplifier. Connect a loop compensation network between COMP pin and the GND pin.                  |

| 5   | GND  | -   | Ground.                                                                                                                        |

| 6   | VOUT | 0   | Boost Converter Output.                                                                                                        |

| 7   | EN   | I   | Enable Logic Input. Logic high makes the circuit enabled, and logic low makes it disabled and the device enters shutdown mode. |

| 8   | ILIM | 0   | Adjustable Switch Peak Current Limit. Connect an external resistor between ILIM pin and the GND pin.                           |

| 9   | VIN  | I   | IC Power Supply Input.                                                                                                         |

| 10  | воот | 0   | Power Supply for High-side MOSFET Gate Driver. Connect a capacitor between the BOOT pin and the SW pin.                        |

| 11  | SW   | I   | Switching Node Pin. Drain connection of low-side power MOSFET and source connection of the high-side power MOSFET.             |

NOTE: I = input, O = output.

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.7 \text{V to } 5.5 \text{V}, V_{OUT} = 9 \text{V}. \text{ Full } = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ typical values are at } T_{J} = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                                                 |           | SYMBOL               | CONDITIONS                                                  | TEMP  | MIN   | TYP   | MAX   | UNITS  |

|---------------------------------------------------------------------------|-----------|----------------------|-------------------------------------------------------------|-------|-------|-------|-------|--------|

| Power Supply                                                              |           |                      |                                                             |       |       |       |       | •      |

| Input Voltage Range                                                       |           | V <sub>IN</sub>      |                                                             | Full  | 2.7   |       | 12    | V      |

|                                                                           |           |                      |                                                             | +25°C |       | 2.5   | 2.62  |        |

| VIN Under-Voltage Lockout Threshold  VIN Under-Voltage Lockout Hysteresis |           | $V_{IN\_UVLO}$       | V <sub>IN</sub> rising                                      | Full  |       | 2.5   | 2.7   | V      |

|                                                                           |           |                      | V <sub>IN</sub> falling                                     | +25°C |       | 2.4   |       | 1      |

| VIN Under-Voltage Lockout Hyster                                          | esis      | V <sub>IN_HYS</sub>  |                                                             | +25°C |       | 100   |       | mV     |

| VCC Regulation                                                            |           | V <sub>cc</sub>      | I <sub>CC</sub> = 5mA, V <sub>IN</sub> = 8V                 | +25°C |       | 5     |       | V      |

| VCC Under-Voltage Lockout Thres                                           | hold      | V <sub>CC_UVLO</sub> | V <sub>CC</sub> falling                                     | +25°C |       | 2.1   |       | V      |

|                                                                           | VINI Dire |                      |                                                             | +25°C |       | 0.23  | 0.4   |        |

| Out and the second of the second of                                       | VIN Pin   |                      | IC enabled, no load, V <sub>FB</sub> = 1.3V,                | Full  |       | 0.23  | 0.5   |        |

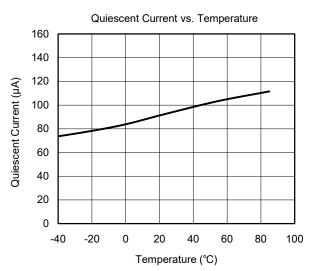

| Operating Quiescent Current                                               | VOLIT Dia | lα                   | V <sub>OUT</sub> = 12V                                      | +25°C |       | 90    | 130   | μA     |

|                                                                           | VOUT Pin  |                      |                                                             | Full  |       | 90    | 160   |        |

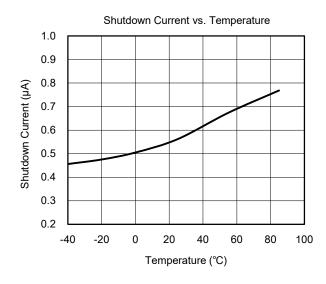

| Chutdown Current into the \/INI Dia                                       |           | ı                    | \/ = 2.6\/ \C dipabled                                      | +25°C |       | 0.6   | 1.1   | ι, Λ   |

| Shutdown Current into the VIN Pin                                         |           | I <sub>SHDN</sub>    | V <sub>IN</sub> = 3.6V, IC disabled                         | Full  |       | 0.6   | 1.5   | μA     |

| Output                                                                    |           |                      |                                                             |       |       |       |       |        |

| Output Voltage Range                                                      |           | V <sub>OUT</sub>     |                                                             | Full  | 4.5   |       | 12.6  | V      |

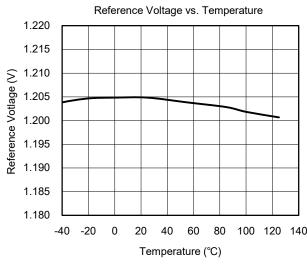

| Deference Voltage at the ED Din                                           |           | \/                   | PWM mode                                                    | Full  | 1.181 | 1.205 | 1.229 | V      |

| Reference Voltage at the FB Pin                                           |           | $V_{REF}$            | PFM mode                                                    | +25°C |       | 1.207 |       | v      |

| Leakage Current into the FB Pin                                           |           | I <sub>FB_LKG</sub>  | V <sub>FB</sub> = 1.2V                                      | +25°C |       | 10    | 100   | nA     |

| Output Over-Voltage Protection Threshold                                  |           | V <sub>OVP</sub>     | V <sub>OUT</sub> rising                                     | Full  | 12.95 | 13.2  | 13.55 | V      |

| Output Over-Voltage Protection Hy                                         | steresis  | V <sub>OVP_HYS</sub> | V <sub>OUT</sub> falling below V <sub>OVP</sub>             | +25°C |       | 0.15  |       | V      |

| Soft Startup Time                                                         |           | t <sub>ss</sub>      | $C_{OUT}$ (effective) = 47 $\mu$ F, $I_{OUT}$ = 0A          | +25°C |       | 4     |       | ms     |

| Error Amplifier                                                           |           |                      |                                                             |       |       |       |       |        |

| COMP Pin Sink Current                                                     |           | I <sub>SINK</sub>    | $V_{FB} = V_{REF} + 100$ mV, $V_{COMP} = 1.2$ V             | +25°C |       | 120   |       | μΑ     |

| COMP Pin Source Current                                                   |           | I <sub>SOURCE</sub>  | $V_{FB} = V_{REF} - 100 \text{mV}, V_{COMP} = 1.2 \text{V}$ | +25°C |       | 15    |       | μΑ     |

| High Clamp Voltage at the COMP                                            | Pin       | $V_{CCLPH}$          | $V_{FB} = 1.1V, R_{ILIM} = 127k\Omega$                      | +25°C |       | 2     |       | V      |

| Low Clamp Voltage at the COMP I                                           | Pin       | V <sub>CCLPL</sub>   | $V_{FB}$ = 1.3V, $R_{ILIM}$ = 127k $\Omega$                 | +25°C |       | 0.4   |       | V      |

| Error Amplifier Transconductance                                          |           | $G_{EA}$             | V <sub>COMP</sub> = 1.2V                                    | +25°C |       | 135   |       | μS     |

| Power Switch                                                              |           |                      |                                                             |       |       |       |       |        |

| High-side MOSFET On-Resistance                                            | 2         |                      | V <sub>CC</sub> = 5V                                        | +25°C |       | 27    | 34    | mΩ     |

| Trigit-side MOOI ET OII-Resistance                                        |           | R <sub>DS(ON)</sub>  | VCC - 3V                                                    | Full  |       | 27    | 44    | 11122  |

| Low-side MOSFET On-Resistance                                             |           | TOS(ON)              | V <sub>CC</sub> = 5V                                        | +25°C |       | 15    | 20    | mΩ     |

| Low-side MOSI ET Off-Resistance                                           |           |                      | VCC - 3V                                                    | Full  |       | 15    | 26    | 11122  |

| Switching Frequency                                                       |           |                      | <del>,</del>                                                |       |       |       |       |        |

| Switching Frequency                                                       |           | f <sub>sw</sub>      |                                                             | +25°C | 980   | 1100  | 1270  | kHz    |

| Switching Frequency                                                       |           | 1900                 |                                                             | Full  | 930   | 1100  | 1320  | IXI IZ |

| Minimum On-Time                                                           |           | t <sub>ON_MIN</sub>  | V <sub>CC</sub> = 5V                                        | +25°C |       | 120   |       | ns     |

| Current Limit                                                             |           |                      |                                                             |       | 1     | r     | 1     | 1      |

| Switch Peak Current Limit                                                 |           | I <sub>LIM</sub>     | $R_{ILIM} = 127k\Omega$                                     | +25°C | 8.5   | 9.5   | 10.8  | Α      |

| Reference Voltage at the ILIM Pin                                         |           | $V_{ILIM}$           |                                                             | +25°C |       | 1.205 |       | V      |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 2.7 \text{V to } 5.5 \text{V}, V_{OUT} = 9 \text{V}. \text{ Full } = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ typical values are at } T_{J} = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                   | SYMBOL              | CONDITIONS                                   | TEMP  | MIN | TYP | MAX | UNITS |  |

|-----------------------------|---------------------|----------------------------------------------|-------|-----|-----|-----|-------|--|

| EN Logic Input              |                     |                                              |       |     |     |     |       |  |

| EN Logic High Threshold     | $V_{ENH}$           |                                              | Full  | 1.2 |     |     | V     |  |

| EN Logic Low Threshold      | V <sub>ENL</sub>    |                                              | Full  |     |     | 0.4 | V     |  |

| EN Pull-Down Resistor       | R <sub>EN</sub>     |                                              | +25°C |     | 800 |     | kΩ    |  |

| Thermal Shutdown            |                     |                                              |       |     |     |     |       |  |

| Thermal Shutdown Threshold  | T <sub>SD</sub>     | T <sub>J</sub> rising                        |       |     | 160 |     | °C    |  |

| Thermal Shutdown Hysteresis | T <sub>SD_HYS</sub> | T <sub>J</sub> falling below T <sub>SD</sub> |       |     | 20  |     | °C    |  |

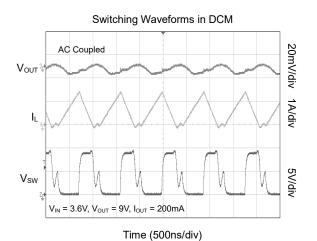

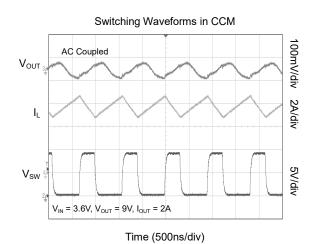

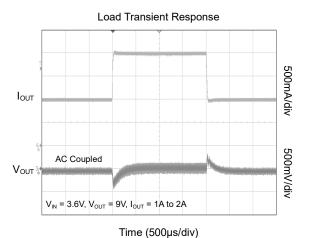

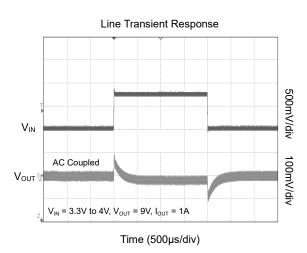

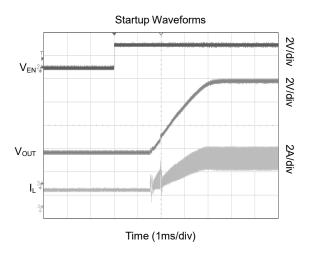

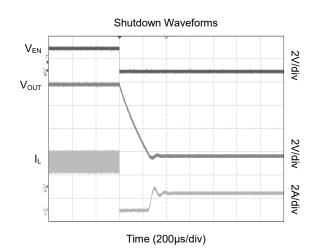

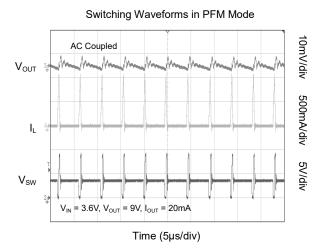

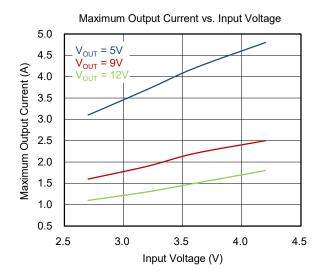

## TYPICAL PERFORMANCE CHARACTERISTICS

At  $T_J = +25$ °C,  $V_{IN} = 3.6$ V,  $V_{OUT} = 9$ V, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

At  $T_J = +25$ °C,  $V_{IN} = 3.6$ V,  $V_{OUT} = 9$ V, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

At  $T_J$  = +25°C,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 9V, unless otherwise noted.

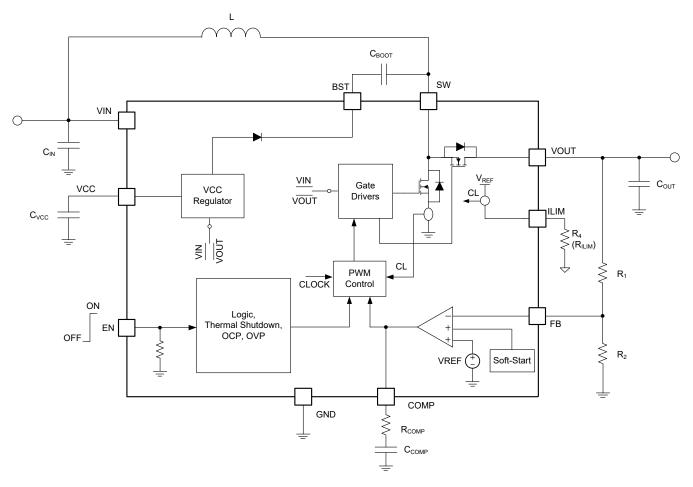

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

## **DETAILED DESCRIPTION**

The SGM6611C is a synchronous Boost converter with two integrated power FETs and is capable of delivering up to 9.5A (TYP) switch current. The device adopts the 1.1MHz fixed frequency peak current mode control architecture to regulate the output voltage. The SGM6611C automatically operates in pulse frequency modulation (PFM) mode at light load to improve the efficiency. As the load current increases, the device enters PWM operation to provide a fixed switching frequency. The device can offer excellent line and load transient responses, in addition, the compensation network is configured externally which brings flexibility to applications with different output capacitor and inductor selections. The device also implements various protection features such as cycle-by-cycle current limit for abnormal load conditions, output over-voltage protection and thermal shutdown.

#### **Enable and Disable**

The input voltage applied to SGM6611C needs to be higher than the maximum UVLO threshold of 2.5V and the EN pin voltage is higher than 1.2V to enable the device. Pulling the EN pin below 0.4V disables the device, where all internal blocks are turned off, and no voltage is present on VCC pin. While disabled, the device stops switching and enters shutdown mode with less than 1.1µA current consumed. VIN and VOUT are connected through the body diode of the high-side rectifier FET in the shutdown mode.

### **Adjustable Peak Current Limit**

The peak current mode control provides inherent over-current protection as the device monitors the changes of inductor current. As the peak current reaches 9.5A (TYP), the device stops switching and turning off the low-side FET to stop inductor current to rise. The peak current limit threshold is programmable via a resistor connected on ILIM pin to ground. Use Equation below to calculate the desired current limit threshold.

$$I_{LIM} = \frac{1.2 \times 10^6}{R_{ILIM}}$$

(1)

where R<sub>ILIM</sub> is the resistor connected between the ILIM

pin and ground, and  $I_{\text{LIM}}$  is the peak current limit.

When  $I_{\text{LIM}}$  is 9.5A (TYP), the value of the resistor is  $127k\Omega.$

#### Soft-Start

The SGM6611C implements internal soft-start function of 4ms (TYP). When enabled, the device slowly ramps the reference voltage to prevent large inrush current during startup.

## Over-Voltage Protection (OVP)

The device implements over-voltage protection to prevent the device from damage and protect the device connected to the output of SGM6611C. When the voltage present on the VOUT pin exceeds 13.2V (TYP), the device stops switching immediately to prevent the output voltage from rising. As the output voltage drops below 150mV (TYP) of hysteresis voltage that is lower than the OVP threshold, the device resumes operation.

## **Under-Voltage Lockout (UVLO)**

An under-voltage lockout (UVLO) circuit prevents the device from malfunctioning at low input voltage and the battery from excessive discharge. The SGM6611C has both VIN UVLO function and VCC UVLO function. It disables the device from switching when the falling voltage at the VIN pin trips the UVLO threshold  $V_{\text{IN\_UVLO}}$ , which is typically 2.4V. The input UVLO function implements a 100mV hysteresis to prevent the false turn-on due to line voltage variations, where the device cannot be turned on until the input voltage increases to 2.5V or higher. When the falling voltage at the VCC pin trips the UVLO threshold  $V_{\text{CC\_UVLO}}$ , typically 2.1V, the device is also disabled.

#### **Thermal Shutdown**

A thermal shutdown function is implemented to prevent damage caused by excessive heat and power dissipation. Once a junction temperature of +160°C (TYP) is exceeded, the device is shut down. The device is released from shutdown automatically when the junction temperature decreases by 20°C.

## **DETAILED DESCRIPTION (continued)**

#### **Device Functional Modes**

#### Operation

The SGM6611C adopts the fixed frequency pulse width modulation (PWM) mode in moderate to heavy load condition. At the start of each clock cycle, the low-side power FET is turned on to ramp up the inductor current until the inductor current reaches the level determined by the output of the internal error amplifier. When the current is reached, LS FET is turned off, and a dead time is issued which is used to prevent shoot-through. During the dead time, the inductor current flows through the body diode of the high-side FET. As the dead time ends, the high-side FET is turned on to ramp down the inductor current to replenish the output capacitor and deliver current to the load. This cycle repeats with a 1.1MHz switching frequency.

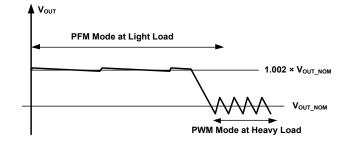

#### **PFM Mode**

In order to improve the light load efficiency, the SGM6611C implements PFM operation at light load. At light load, the internal error amplifier's output decreases to lower the inductor current. As the current reaches zero during the low-side off-time, the high-side FET turns off till the next switching cycle starts. As the load current decreases further, the output of the error

amplifier reaches a voltage that is corresponds to  $I_{LIM}/10$ . The output of the error amplifier is clamped at this value and no longer decreases. The SGM6611C automatically adjusts the off-time in PFM mode to meet the load demand, and lower load current results in longer off-time. The output voltage is regulated to 0.2% higher than the nominal programmed output voltage at PFM mode. The SGM6611C is capable of achieving above 70% efficiency when the load current is less than 1mA. Output voltage ripple is also lower in PFM mode since the peak inductor current is lower.

Figure 3. Output Voltage in PWM Mode and PFM Mode

## APPLICATION INFORMATION

The SGM6611C is capable of supporting up to 12.6V output voltage, while providing 9.5A (TYP) continuous switch current. The device automatically operates in PFM mode in light load. At medium to heavy load, the device switches to PWM operation. PFM mode provides high light load efficiency while PWM mode provides constant switching frequency. The fixed frequency peak current mode control offers excellent line and load transient responses. The external loop compensation enables design flexibility with various inductor and output capacitor combinations.

**Table 1. Design Parameters**

| Design Parameters            | Example Values     |

|------------------------------|--------------------|

| Input Voltage Range          | 3.0V to 4.35V      |

| Output Voltage               | 9V                 |

| Output Voltage Ripple        | 100mV peak-to-peak |

| Output Current Rating        | 1.5A               |

| Operating Frequency          | 1.1MHz             |

| Operation Mode at Light Load | PFM (SGM6611C)     |

## **Setting Peak Current Limit**

The peak current limit is programmed via an external resistor on ILIM pin. The resistor value can be calculated by Equation 2:

$$I_{LIM} = \frac{1.2 \times 10^6}{R_{ILIM}}$$

(2)

where  $R_{\text{ILIM}}$  is the resistor connected between the ILIM pin and ground, and  $I_{\text{LIM}}$  is the switching peak current limit

A standard  $127k\Omega$  provides the 9.5A typical current limit. Considering variation due to tolerance and temperature, the worst-case required peak current should be lower than the minimal current limit rating to ensure that the SGM6611C can regulate the output voltage. For Boost converter, the worst case occurs at the lowest VIN and the highest load current.

Figure 4. SGM6611C Single-Cell Li-Ion Battery to 9V/1.5A Output Converter

## **Setting Output Voltage**

The output voltage of SGM6611C is programmed by a resistive divider connected to FB pin. Use Equation below to program the output voltage. R1 is the top feedback resistor and R2 is the bottom feedback resistor. The recommended value for R2 should be less than  $120k\Omega$ .

$$R_1 = \frac{(V_{OUT} - V_{REF}) \times R_2}{V_{REF}}$$

(3)

#### **Inductor Selection**

Inductor is an essential element for DC/DC switch mode power supplies regardless of topology. Inductor serves as the energy storage element for power conversion. Inductance and inductor's saturation current are the two most important criterions for inductor selection. For general rule of thumb, the selected inductance should provide a peak-to-peak ripple current that is around 30% of the average inductor current at full load and nominal input voltage. The average inductor current for a Boost converter is the input current. The SGM6611C is optimized to operate with inductor values between 0.47µH and 2.2µH. Lower inductance part generally has smaller size while providing sufficient saturation current rating, and larger inductance provides lower peak-to-peak ripple current, which helps to maximize the output current delivery.

Equations 4 to 6 show the calculated key parameters for selecting the inductor. The selected inductor should meet the worst case that occurs at minimum input voltage and maximal load current. Margin should be added to cover inductance de-rating and conversion

efficiency.

For Boost converter, the average inductor current is the average input current, Equation 4 is used to calculate the average inductor current:

$$I_{DC} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta}$$

(4)

where  $V_{\text{OUT}}$  is the output voltage,  $I_{\text{OUT}}$  is the output current,  $V_{\text{IN}}$  is the input voltage, and  $\eta$  is the power conversion efficiency.

Use Equation 5 below to set the inductor current peak-to-peak ripple.

$$I_{PP} = \frac{1}{L \times (\frac{1}{V_{OUT} - V_{IN}} + \frac{1}{V_{IN}}) \times f_{SW}}$$

(5)

where  $I_{PP}$  is the inductor peak-to-peak ripple, L is the inductor value,  $f_{SW}$  is the switching frequency,  $V_{OUT}$  is the output voltage, and  $V_{IN}$  is the input voltage.

The peak inductor current is the sum of average current plus half of the peak-to-peak inductor current shown in Equation 6:

$$I_{LPEAK} = I_{DC} + \frac{I_{PP}}{2} \tag{6}$$

The selected inductor should have the saturation current rating higher than the calculated peak current, and the calculated peak current should be lower than the peak current limit of SGM6611C.

Inductor's DCR, material type, DC/DC's power FET resistance and switching speed affect the overall efficiency of the converter, therefore, careful inductor selection is critical to ensure good performance.

Table 2 lists the recommended inductors for SGM6611C.

Table 2. Recommended Inductors

| Part Number       | L<br>(µH) | DCR MAX<br>(mΩ) | Saturation Current/<br>Heat Rating Current (A) | Size MAX<br>(L mm × W mm × H mm) | Manufacturer     |

|-------------------|-----------|-----------------|------------------------------------------------|----------------------------------|------------------|

| HTTH25201T-1R0MSR | 1.0       | 29              | 5.0/5.0                                        | 2.5 × 2.0 × 1.0                  | Cyntec           |

| 74439344010       | 1.0       | 5.5             | 27.5/12                                        | 6.65 × 6.45 × 3.0                | Wurth-Elektronik |

| 744311150         | 1.5       | 7.2             | 14.0/11.0                                      | 7.3 × 7.2 × 4.0                  | Wurth-Elektronik |

| CDMC8D28NP-1R8MC  | 1.8       | 12.6            | 9.4/9.3                                        | 9.5 × 8.7 × 3.0                  | Sumida           |

| 744325180         | 1.8       | 3.5             | 18/14                                          | 10.5 × 10.2 × 4.7                | Wurth-Elektronik |

| 744311220         | 2.2       | 12.5            | 13.0/9.0                                       | 7.3 × 7.2 × 4.0                  | Wurth-Elektronik |

| PIMB103T-2R2MS    | 2.2       | 9.0             | 16/13                                          | 11.2 × 10.3 × 3.0                | Cyntec           |

| PIMB065T-2R2MS    | 2.2       | 12.5            | 12/10.5                                        | 7.4 × 6.8 × 5.0                  | Cyntec           |

## **Input Capacitor Selection**

Boost converter's input capacitor has continuous current throughout the entire switching cycle. A  $10\mu F$  ceramic capacitor is recommended to place between the VIN pin and GND pin of SGM6611C as close as possible. For the applications where the SGM6611C is located far away from the input source, a  $47\mu F$  or higher capacitance capacitor is recommended to damp the wiring harness's inductance.

The VCC pin is the output of the internal regulator, a  $1\mu F$  ceramic capacitor is recommended to place on the VCC pin.

## **Output Capacitor Selection**

The output capacitors of Boost converter dictate the

output voltage ripple and load transient response. Equation 7 is used to estimate the necessary capacitance to achieve the desired output voltage ripple, where  $\Delta V$  is the maximum allowed ripple. Three 22 $\mu$ F ceramic output capacitors are recommended for SGM6611C. Due to the DC de-rating effect of the ceramic capacitor, margin should be considered, where higher capacitance improves the transient response.

$$V_{RIPPLE\_DIS} = \frac{(V_{OUT} - V_{IN\_MIN}) \times I_{OUT}}{V_{OLT} \times f_{SW} \times C_{OLT}}$$

(7)

ESR of the output capacitor affects the output ripple. Use Equation 8 to set the output ripple caused by ESR.

$$V_{RIPPLE ESR} = I_{LPEAK} \times R_{ESR}$$

(8)

## **Loop Stability**

The compensation network of SGM6611C is completed externally to improve design flexibility. The SGM6611C implements a transconductance error amplifier, where the COMP pin is the output of the internal error amplifier. A Type-II compensation network consisting of R5, C5 and C6 connected on COMP pin is used to configure the loop response of SGM6611C.

The power stage small signal loop response for peak current control can be shown by Equation 9.

$$G_{PS}(S) = \frac{R_{o} \times (1-D)}{2 \times R_{SENSE}} \times \frac{(1 + \frac{S}{2 \times \pi \times f_{ESRZ}})(1 - \frac{S}{2 \times \pi \times f_{RHPZ}})}{1 + \frac{S}{2 \times \pi \times f_{D}}}$$

(9)

where D is the switching duty cycle,  $R_O$  is the output load resistance,  $R_{SENSE}$  is the equivalent internal current sense resistor, which is  $0.08\Omega$ .  $f_P$  is the pole's frequency,  $f_{ESRZ}$  is the zero's frequency, and  $f_{RHPZ}$  is the right-half-plane-zero's frequency.

The D,  $f_P$ ,  $f_{ESRZ}$  and  $f_{RHPZ}$  can be set by following equations.

$$D = 1 - \frac{V_{IN} \times \eta}{V_{OUT}}$$

(10)

where  $\eta$  is the power conversion efficiency.

$$f_{P} = \frac{2}{2\pi \times R_{O} \times C_{OUT}}$$

(11)

where  $C_{\text{OUT}}$  is effective capacitance of the output capacitor.

$$f_{\text{ESRZ}} = \frac{1}{2\pi \times R_{\text{ESR}} \times C_{\text{OUT}}}$$

(12)

where  $R_{\text{ESR}}$  is the equivalent series resistance of the output capacitor.

$$f_{RHPZ} = \frac{R_O \times (1-D)^2}{2\pi \times L}$$

(13)

Equation 14 shows the small signal transfer function of the compensation network.

$$G_{c}(S) = \frac{G_{EA} \times R_{EA} \times V_{REF}}{V_{OUT}} \times \frac{(1 + \frac{S}{2 \times \pi \times f_{COMZ}})}{(1 + \frac{S}{2 \times \pi \times f_{COMP1}})(1 + \frac{S}{2 \times \pi \times f_{COMP2}})}$$

(14)

where  $G_{EA}$  is the amplifier's transconductance,  $R_{EA}$  is the amplifier's output resistance,  $V_{REF}$  is the reference voltage at the FB pin,  $V_{OUT}$  is the output voltage,  $f_{COMP1}$ ,  $f_{COMP2}$  are the pole's frequency of the compensation network, and  $f_{COMZ}$  is the zero's frequency of the compensation network.

Once the error amplifier and power stage's poles and zeros are determined, the compensation network's component value can be designed. The designed loop crossover frequency  $f_C$  should be within 1/5 of the RHPZ frequency  $(f_{RHPZ})$  or 1/10 of the switching frequency. Higher crossover frequency could improve the transient response. However, the crossover frequency should be designed to avoid instability.

With a selected  $f_C$ , Equation 15 can be used to calculate the required R5.

$$R_{5} = \frac{2\pi \times V_{\text{OUT}} \times R_{\text{SENSE}} \times f_{\text{C}} \times C_{\text{OUT}}}{(1-D) \times V_{\text{RFF}} \times G_{\text{FA}}}$$

(15)

Use Equation 16 to calculate the value of C<sub>5</sub>.

$$C_5 = \frac{R_0 \times C_{OUT}}{2R_5} \tag{16}$$

Use Equation 17 to calculate the value of C<sub>6</sub>.

$$C_6 = \frac{R_{ESR} \times C_{OUT}}{R_5}$$

(17)

For application with only ceramic capacitor, or if the calculated value of  $C_6$  is less than 10pF,  $C_6$  is not needed.

To measure good loop compensation design, greater than 45° of phase margin and greater than 10dB gain margin could provide good loop stability and avoid output voltage ringing during load and line transient.

## **Layout Guidelines**

In addition to component selection, layout is a critical step to ensure the performance of any switch mode power supplies. Poor layout could result in system instability, EMI failure, and device damage. Thus, place the inductor, input and output capacitors as close to the IC as possible, and use wide and short traces for current carrying traces to minimize PCB inductance.

For Boost converter, the output capacitor's current loop from VOUT pin back to the GND pin of the device should be as small as possible. Use small traces and small copper area of all traces connected to the SW node to minimize SW node vias and to prevent radiation of high-frequency noise. It is also recommended to place a ground plane below the DC/DC to minimize inter plane coupling.

Figure 5. Layout Example

## **SGM6611C**

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DECEMBER 2022 – REV.B.1 to REV.B.2                                                              | Page               |

|-------------------------------------------------------------------------------------------------|--------------------|

| Updated Maximum Output Current vs. Input Voltage in Typical Performance Characteristics section | 8                  |

| JULY 2022 – REV.B to REV.B.1                                                                    | Page               |

| Added SW Node in Absolute Maximum Ratings                                                       | 2                  |

| Updated Detailed Description and Application Information sections                               | 10, 11, 12, 13, 14 |

| OCTOBER 2021 – REV.A.4 to REV.B                                                                 | Page               |

| Updated the Enable and Disable section                                                          | 10                 |

| Added the Figure 1. Layout Example                                                              | 16                 |

| APRIL 2021 – REV.A.3 to REV.A.4                                                                 | Page               |

| Updated Loop Stability section                                                                  | 15                 |

| MARCH 2021 – REV.A.2 to REV.A.3                                                                 | Page               |

| Updated Package Outline Dimensions section                                                      | 17                 |

| FEBRUARY 2021 – REV.A.1 to REV.A.2                                                              | Page               |

| Updated Marking Information section                                                             | 2                  |

| NOVEMBER 2019 – REV.A to REV.A.1                                                                | Page               |

| Updated the curve of Output Current vs. Input Voltage                                           | 8                  |

| Changes from Original (AUGUST 2019) to REV.A                                                    | Page               |

| Changed from product preview to production data                                                 | All                |

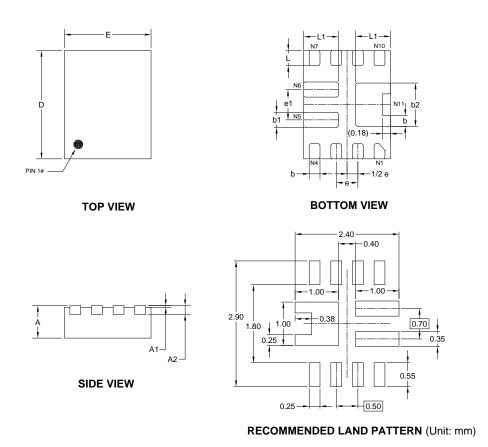

# PACKAGE OUTLINE DIMENSIONS TQFN-2×2.5-11L

| Symbol | Dimensions In Millimeters |           |       |  |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|--|

| Symbol | MIN                       | MOD       | MAX   |  |  |  |  |

| Α      | 0.700                     | 0.750     | 0.800 |  |  |  |  |

| A1     | 0.000                     | 0.020     | 0.050 |  |  |  |  |

| A2     |                           | 0.203 REF |       |  |  |  |  |

| D      | 2.400                     | 2.500     | 2.600 |  |  |  |  |

| E      | 1.900                     | 2.000     | 2.100 |  |  |  |  |

| е      | 0.500 BSC                 |           |       |  |  |  |  |

| e1     |                           | 0.700 BSC |       |  |  |  |  |

| b      | 0.200                     | 0.250     | 0.300 |  |  |  |  |

| b1     | 0.300 0.350               |           | 0.400 |  |  |  |  |

| b2     | 0.950                     | 1.000     | 1.050 |  |  |  |  |

| L      | L 0.300 0.350             |           | 0.400 |  |  |  |  |

| L1     | 0.750                     | 0.800     | 0.850 |  |  |  |  |

NOTE: This drawing is subject to change without notice.

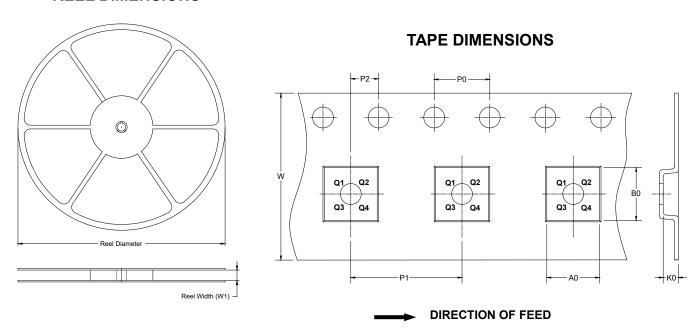

## TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type   | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-2×2.5-11L | 7"               | 9.5                      | 2.20       | 2.70       | 0.95       | 4.0        | 4.0        | 2.0        | 8.0       | Q2               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-------------|----------------|---------------|----------------|--------------|

| 7" (Option) | 368            | 227           | 224            | 8            |

| 7"          | 442            | 410           | 224            | 18           |